# HMC625BLP5E

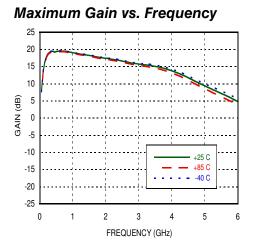

## 0.5 dB LSB GaAs MMIC 6-BIT DIGITAL VARIABLE GAIN AMPLIFIER, DC - 5 GHz

### **Typical Applications**

The HMC625BLP5E is ideal for:

- Cellular/3G Infrastructure

- WiBro / WiMAX / 4G

- Microwave Radio & VSAT

- Test Equipment and Sensors

- IF & RF Applications

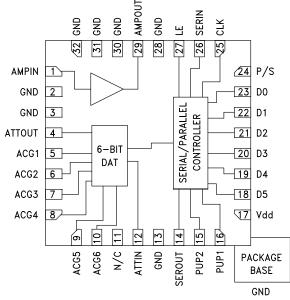

#### **Functional Diagram**

#### Features

-13.5 to +18 Gain Control in 0.5 dB Steps Power-up State Selection High Output IP3: +32 dBm TTL/CMOS Compatible Serial, Parallel, or latched Parallel Control ±0.25 dB Typical Gain Step Error Single +5V Supply 32 Lead 5x5 mm SMT Package: 25 mm<sup>2</sup>

#### **General Description**

The HMC625BLP5E is a digitally controlled variable gain amplifier which operates from DC to 5 GHz, and can be programmed to provide anywhere from 13.5 dB attenuation, to 18 dB of gain, in 0.5 dB steps. The HMC625BLP5E delivers noise figure of 6 dB in its maximum gain state, with output IP3 of up to +32 dBm in any state. The dual mode control interface is CMOS/TTL compatible, and accepts either a three wire serial input or a 6 bit parallel word. The HMC625BLP5E also features a user selectable power up state and a serial output port for cascading other Hittite serial controlled components. The HMC625BLP5E is housed in a RoHS compliant 5x5 mm QFN leadless package, and requires no external matching components.

#### Electrical Specifications, $T_{a} = +25^{\circ}$ C, 50 Ohm System, Vdd= +5V, Vs= +5V

| Parameter                                                                                     | Frequency                     | Min.                                                                             | Тур.     | Max.     | Units      |

|-----------------------------------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------|----------|----------|------------|

| Gain (Maximum Gain State)                                                                     | DC - 3.0 GHz<br>3.0 - 5.0 GHz | 13<br>5                                                                          | 18<br>13 |          | dB<br>dB   |

| Gain Control Range                                                                            |                               |                                                                                  | 31.5     |          | dB         |

| Input Return Loss                                                                             | DC - 5.0 GHz                  |                                                                                  | 15       |          | dB         |

| Output Return Loss                                                                            | DC - 5.0 GHz                  |                                                                                  | 10       |          | dB         |

| Gain Accuracy: (Referenced to Maximum Gain State)<br>All Gain States                          | DC - 0.8 GHz<br>0.8 - 5.0 GHz | $\pm$ (0.10 + 5% of Gain Setting) Max.<br>$\pm$ (0.30 + 3% of Gain Setting) Max. |          | dB<br>dB |            |

| Output Power for 1dB Compression                                                              | DC - 3.0 GHz<br>3.0 - 5.0 GHz | 16<br>13                                                                         | 19<br>16 |          | dBm<br>dBm |

| Output Third Order Intercept Point<br>(Two-Tone Output Power= 0 dBm Each Tone, 1 MHz Spacing) | DC - 5.0 GHz                  |                                                                                  | 32       |          | dBm        |

| Noise Figure                                                                                  | 900 MHz                       |                                                                                  | 6        |          | dB         |

| Total Supply Current (Idd + Is)                                                               | DC - 5.0 GHz                  | 60                                                                               | 87.5     | 100      | mA         |

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

For price, delivery, and to place orders: Analog Devices, Inc., One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106 Phone: 781-329-4700 • Order online at www.analog.com Application Support: Phone: 1-800-ANALOG-D

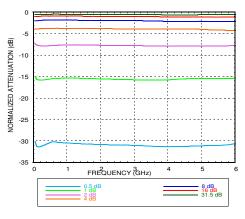

#### Normalized Attenuation

(Only Major States are Shown)

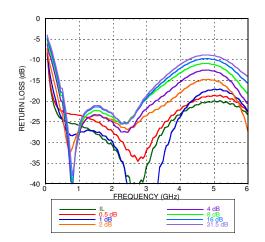

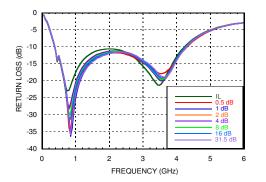

Input Return Loss (Only Major States are Shown)

**Output Return Loss**

(Only Major States are Shown)

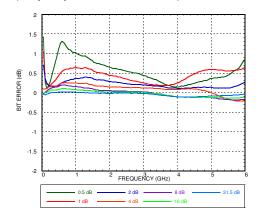

#### Bit Error vs. Frequency (Only Major States are Shown)

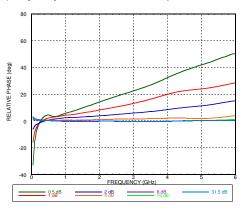

Normal Relative Phase vs. Frequency (Only Major States are Shown)

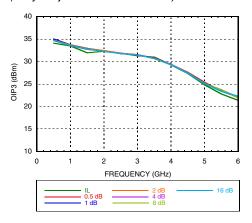

**Output IP3 vs. Attenuation Settings** (Only Major States are Shown)

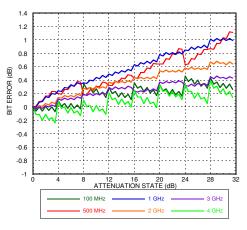

Bit Error vs. Attenuation State

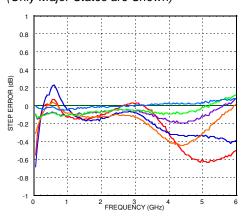

**Step Error vs. Frequency** (Only Major States are Shown)

## HMC625BLP5E

v02.0616

## 0.5 dB LSB GaAs MMIC 6-BIT DIGITAL VARIABLE GAIN AMPLIFIER, DC - 5 GHz

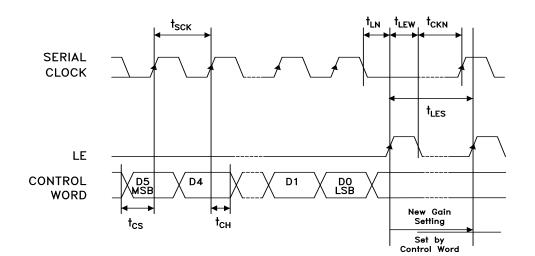

#### Serial Control Interface

The HMC625BLP5E contains a 3-wire SPI compatible digital interface (SERIN, CLK, LE). It is activated when P/S is kept high. The 6-bit serial word must be loaded MSB first. The positive-edge sensitive CLK and LE requires clean transitions. If mechanical switches were used, sufficient debouncing should be provided. When LE is high, 6-bit data in the serial input register is transferred to the attenuator. When LE is high CLK is masked to prevent data transition during output loading.

When P/S is low, 3-wire SPI interface inputs (SERIN, CLK, LE) are disabled and serial input register is loaded asynchronously with parallel digital inputs (D0-D5). When LE is high, 6-bit parallel data is transferred to the attenuator.

For all modes of operations, the DVGA state will stay constant while LE is kept low.

| Parameter                                    | Тур.   |

|----------------------------------------------|--------|

| Min. serial period, $t_{_{SCK}}$             | 100 ns |

| Control set-up time, t <sub>cs</sub>         | 20 ns  |

| Control hold-time, t <sub>CH</sub>           | 20 ns  |

| LE setup-time, t <sub>LN</sub>               | 10 ns  |

| Min. LE pulse width, t <sub>LEW</sub>        | 10 ns  |

| Min LE pulse spacing, t <sub>LES</sub>       | 630 ns |

| Serial clock hold-time from LE, $t_{CKN}$    | 10 ns  |

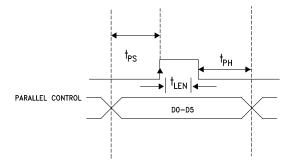

| Hold Time t <sub>PH</sub>                    | 0 ns   |

| Latch Enable Minimum width, $t_{\text{LEN}}$ | 10 ns  |

| Setup Time, t <sub>PS</sub>                  | 2 ns   |

#### Timing Diagram (Latched Parallel Mode)

#### Parallel Mode (Direct Parallel Mode & Latched Parallel Mode)

Note: The parallel mode is enabled when P/S is set to low.

**Direct Parallel Mode** - The attenuation state is changed by the Control Voltage Inputs directly. The LE (Latch Enable) must be at a logic high to control the attenuator in this manner.

Latched Parallel Mode - The attenuation state is selected using the Control Voltage Inputs and set while the LE is in the Low state. The attenuator will not change state while LE is Low. Once all Control Voltage Inputs are at the desired states the LE is pulsed. See timing diagram above for reference.

#### **Power-Up States**

If LE is set to logic LOW at power-up, the logic state of PUP1 and PUP2 determines the power-up state of the part per PUP truth table. If the LE is set to logic HIGH at power-up, the logic state of D0-D5 determines the power-up state of the part per truth table. The DVGA latches in the desired power-up state approximately 200 ms after power-up.

#### **Power-On Sequence**

The ideal power-up sequence is: GND, Vdd, digital inputs, RF inputs. The relative order of the digital inputs are not important as long as they are powered after Vdd / GND

#### Absolute Maximum Ratings

| •                     |

|-----------------------|

| 11.5 dBm (T = +85 °C) |

| -0.5 to Vdd +0.5V     |

| 5.6V                  |

| 5.5V                  |

| 150 °C                |

| 0.546 W               |

| 119 °C/W              |

| -65 to +150 °C        |

| -40 to +85 °C         |

| Class 1A              |

|                       |

[1] The maximum RF input power increases by the same amount the gain is reduced. The maximum input power at any state is no more than 28 dBm.

[2] This value is the total power dissipation in the amplifier.

[3] This is the thermal resistance for the amplifier.

#### **PUP Truth Table**

| LE | PUP1 | PUP2 | Gain Relative to Maximum<br>Gain |

|----|------|------|----------------------------------|

| 0  | 0    | 0    | -31.5                            |

| 0  | 1    | 0    | -24                              |

| 0  | 0    | 1    | -16                              |

| 0  | 1    | 1    | Insertion Loss                   |

| 1  | х    | х    | 0 to -31.5 dB                    |

Note: The logic state of D0 - D5 determines the power-up state per truth table shown below when LE is high at power-up.

#### **Truth Table**

| Control Voltage Input |                                                                 |      |      |      | Gain |                                |

|-----------------------|-----------------------------------------------------------------|------|------|------|------|--------------------------------|

| D5                    | D4                                                              | D3   | D2   | D1   | D0   | Relative to<br>Maximum<br>Gain |

| High                  | High                                                            | High | High | High | High | 0 dB                           |

| High                  | High                                                            | High | High | High | Low  | -0.5 dB                        |

| High                  | High                                                            | High | High | Low  | High | -1 dB                          |

| High                  | High                                                            | High | Low  | High | High | -2 dB                          |

| High                  | High                                                            | Low  | High | High | High | -4 dB                          |

| High                  | Low                                                             | High | High | High | High | -8 dB                          |

| Low                   | High                                                            | High | High | High | High | -16 dB                         |

| Low                   | Low                                                             | Low  | Low  | Low  | Low  | -31.5 dB                       |

| Any cor               | Any combination of the above states will provide a reduction in |      |      |      |      |                                |

gain approximately equal to the sum of the bits selected.

#### **Control Voltage Table**

| State | Vdd = +3V         | Vdd = +5V         |

|-------|-------------------|-------------------|

| Low   | 0 to 0.5V @ <1 µA | 0 to 0.8V @ <1 µA |

| High  | 2 to 3V @ <1 µA   | 2 to 5V @ <1 µA   |

#### **Bias Voltage**

| Vdd (V) | ldd (Typ.) (mA) |

|---------|-----------------|

| 5V      | 2.5             |

| Vs (V)  | Is (Typ.) (mA)  |

| 5V      | 85              |

ELECTROSTATIC SENSITIVE DEVICE OBSERVE HANDLING PRECAUTIONS

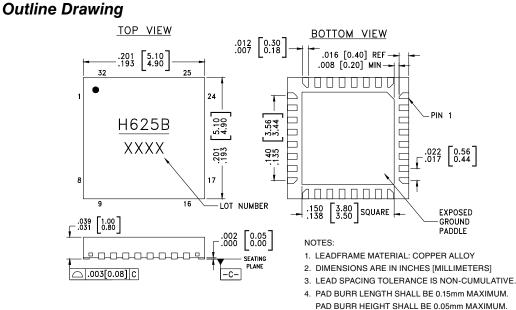

- 5. PACKAGE WARP SHALL NOT EXCEED 0.05mm.

- ALL GROUND LEADS AND GROUND PADDLE MUST BE SOLDERED TO PCB RF GROUND.

7. REFER TO HITTITE APPLICATION NOTE FOR SUGGESTED LAND PATTERN.

#### **Package Information**

| Part Number | Package Body Material                              | Lead Finish   | MSL Rating          | Package Marking <sup>[2]</sup> |

|-------------|----------------------------------------------------|---------------|---------------------|--------------------------------|

| HMC625BLP5E | RoHS-compliant Low Stress Injection Molded Plastic | 100% matte Sn | MSL3 <sup>[1]</sup> | <u>H625B</u><br>XXXX           |

[1] Max peak reflow temperature of 260 °C

[2] 4-Digit lot number XXXX

#### **Pin Descriptions**

| Pin Number               | Function                  | Description                                                                                                                                    | Interface Schematic    |

|--------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| 1                        | AMPIN                     | This pin is DC coupled.<br>An off chip DC blocking capacitor is required.                                                                      |                        |

| 29                       | AMPOUT                    | RF output and DC bias (Vcc) for the output stage of the amplifier.                                                                             |                        |

| 2, 3, 13,<br>28, 30 - 32 | GND                       | These pins and package bottom must be connected to RF/DC ground.                                                                               |                        |

| 4, 12                    | ATTIN,<br>ATTOUT          | These pins are DC coupled and matched to 50 Ohms.<br>Blocking capacitors are required. Select value based<br>on lowest frequency of operation. |                        |

| 5 - 10                   | ACG1 - ACG6               | External capacitors to ground is required. Select value for lowest frequency of operation. Place capacitor as close to pins as possible.       |                        |

| 11                       | N/C                       | The pins are not connected internally; however, all data shown<br>herein was measured with these pins connected to RF/DC ground<br>externally. |                        |

| 14                       | SEROUT                    | Serial input data delayed by 6 clock cycles.                                                                                                   | Vdd<br>Vdd<br>SEROUT   |

| 15, 16                   | PUP2, PUP1                |                                                                                                                                                | Vdd                    |

| 18 - 23                  | D5, D4, D3,<br>D2, D1, D0 |                                                                                                                                                | SERIN                  |

| 24                       | P/S                       |                                                                                                                                                | PUP2,<br>PUP1<br>D0-D5 |

| 25                       | CLK                       |                                                                                                                                                | P/S                    |

| 26                       | SERIN                     |                                                                                                                                                |                        |

| 27                       | LE                        |                                                                                                                                                |                        |

| 17                       | Vdd                       | Supply Voltage                                                                                                                                 |                        |

# HMC625BLP5E

## 0.5 dB LSB GaAs MMIC 6-BIT DIGITAL VARIABLE GAIN AMPLIFIER, DC - 5 GHz

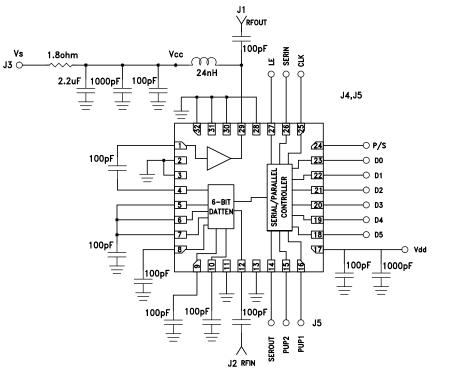

#### **Application Circuit**

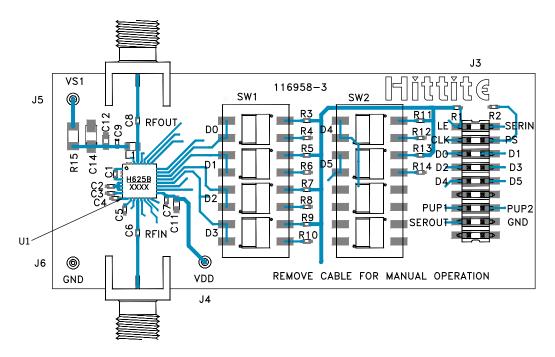

#### **Evaluation PCB**

#### List of Materials for Evaluation PCB 116960 - HMC625BLP5 [1]

| PCB Mount SMA Connector             |

|-------------------------------------|

|                                     |

| 18 Pin DC Connector                 |

| DC Pin                              |

| 100 pF Capacitor, 0402 Pkg.         |

| 1000 pF Capacitor, 0402 Pkg.        |

| 2.2 µF Capacitor, CASE A Pkg.       |

| 100 kOhm Resistor, 0402 Pkg.        |

| 1.8 Ohm Resistor, 1206 Pkg.         |

| SPDT 4 Position DIP Switch          |

| 24 nH Inductor, 0603 Pkg.           |

| HMC625BLP5E Variable Gain Amplifier |

| 116958 Evaluation PCB               |

|                                     |

Reference this number when ordering complete evaluation PCB

Circuit Board Material: Arlon 25FR

The circuit board used in the application should use RF circuit design techniques. Signal lines should have 50 Ohm impedance while the package ground leads and exposed paddle should be connected directly to the ground plane similar to that shown. A sufficient number of via holes should be used to connect the top and bottom ground planes. The evaluation circuit board shown is available from Hittite upon request.

For price, delivery, and to place orders: Analog Devices, Inc., One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106 Phone: 781-329-4700 • Order online at www.analog.com Application Support: Phone: 1-800-ANALOG-D

## **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Analog Devices Inc.: HMC625BLP5E HMC625BLP5ETR 116960-HMC625BLP5